小白也能看懂 半導體制程/工藝/生產的秘密

昨天三星宣布全新的 10nm LPP 工藝已經投產了,而 LPP 工藝相比驍龍835使用的 LPE 工藝,性能提升了10%,功耗下降了15%。但作為一個辣雞小編,其實我是看不太懂的,都是10nm制程,怎么還能提升性能呢?這些 LPP、LPE 都是指的什么,還有之前看到的 FinFET 這些詞又都指的什么?相信和小編有同樣疑問的讀者不在少數(shù),索性今天我們就來刨根問底一番,看看現(xiàn)在火熱的半導體究竟有哪些秘密。

制程的秘密:多少nm很重要嗎?

摩爾定律大家肯定都知道:每過18個月,單位面積上的晶體管數(shù)量增加一倍嘛!然而多年來半導體制程從65nm到32nm,再到28nm,還有近兩年的14nm、16nm和10nm,感覺也沒什么規(guī)律?。∵@里我們就需要認識一下尺寸的計算方式,以及“半代升級”和“整代升級”的概念了。

首先,單位面積內晶體管數(shù)量翻倍并不意味著制程就要縮小一半,縮小一半的話單位面積晶體管數(shù)量不就翻4倍嗎?所以如果要保證兩倍的成長,那么整代升級應該乘以0.7。所以從14nm 到10nm,以及后面從10nm 到7nm,都是遵循了摩爾定律的整代升級。

但是在幾年以前,我們卻經歷過一段“半代升級”的風潮,打破了0.7的規(guī)律。在 40nm 前后幾年,正好是存儲器需求飛速發(fā)展的時間段,考慮到0.9倍的制程升級就能將閃存容量提升1.24倍,且0.9倍的升級技術簡單,半年就能完成,所以不少代工廠開始“半代升級”制程來幫助 NAND 閃存廠商搶占市場。

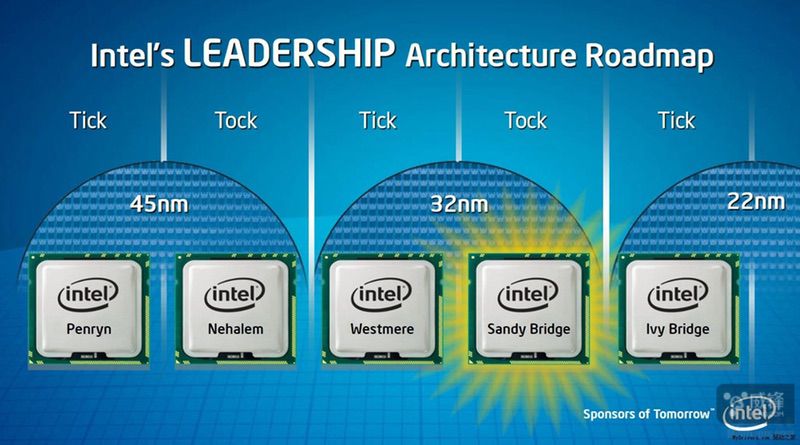

正常來說制程升級應該是45nm—32nm—22nm—14nm—10nm,也就是經典的Tick Tock。但是臺積電當年在 45nm 之后卻推出40nm,這也迫使英特爾和三星等廠商打破了規(guī)律,在2010年前后啟用了 NAND 專屬的 35nm 制程(有趣的是華為海思四核也用了35nm 制程)。而雞賊的臺積電后來又跳到 28nm,搶占制程高地,這顯然讓英特爾和三星很不開心,所以后期三星和英特爾都回到了正常的升級策略,并且從那以后,英特爾就一直對半代升級嗤之以鼻(惱羞成怒)。

而臺積電在堅持了 20nm 和 16nm 兩代之后,也主動回到了 10nm 的正軌。原因非常簡單,因為 NAND 顆粒并不是制程越小性能越好,20nm 之后就會發(fā)生嚴重的電子干擾,所以在 20nm 制程后,各大廠商都轉向了3D NAND 技術(如果大家對閃存有興趣我們今后也可以科普),再往后大家也不在 NAND 的制程上較勁了。

工藝的秘密:這些字母其實很好懂

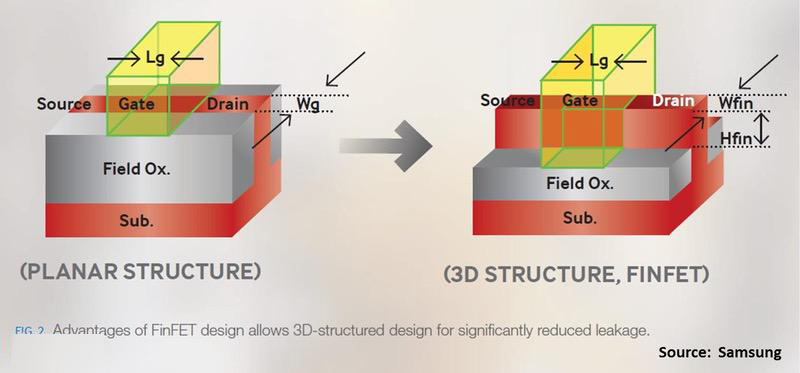

至于后綴的那些英文其實也不難理解,比如 FinFET 工藝(注意哦,多少納米叫制程,而后綴指的是工藝),這一工藝最早由英特爾在22nm 制程時提出,而現(xiàn)在英特爾、臺積電和三星都用的 FinFET 。

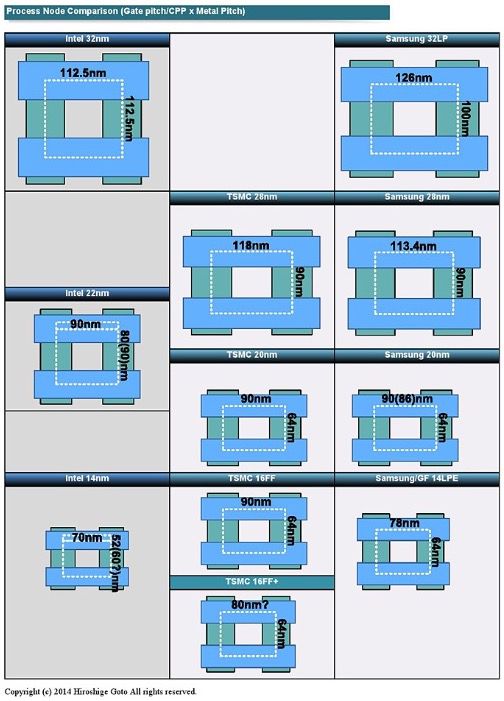

因為制程中 22nm 是指每個晶體管中兩個柵極之間的距離,所以 22nm 并不是指晶體管尺寸,一般一個 22nm 制程的晶體管尺寸高達 90nm ,而柵極間距越小電子流動的時間就越短,所以性能就提升了。但是隨著柵極距離越來越小,絕緣效果就會下降導致漏電,所以每經過幾代制程升級,就需要有一次工藝升級來解決這個問題。FinFET 之前已經有過High-K、HKMG 等工藝了,而 FinFET 之后,我們還會見證 FD-SOI 、GAA的競爭。

至于 FinFET 的原理,它的全稱是“鰭式場效晶體管”,簡單說來就是講柵極之間的絕緣層加高,來增強絕緣效果減少漏電現(xiàn)象,是不是覺得挺傻瓜的?但往往是看起來很簡單的想法,實現(xiàn)起來卻無比困難。

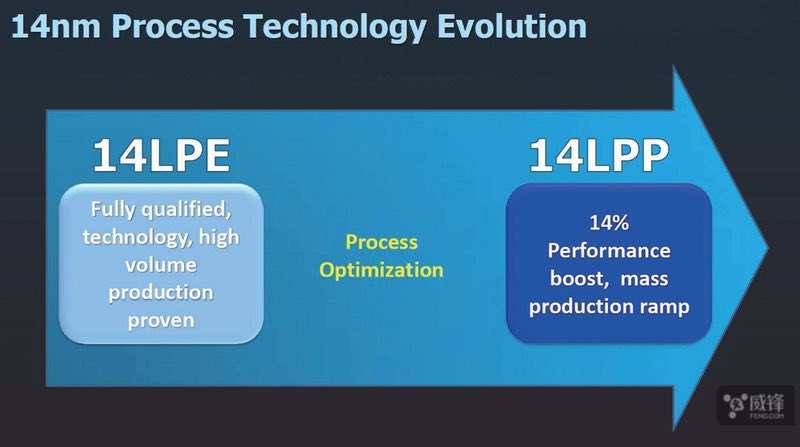

說完了 FinFET,我們還有最后一個后綴,就是昨天報道中的 LPP、LPE 了,其實這些指的都是同一代工藝中的不同種類,比如 LPE(Low Power Early) 指早期低功耗工藝,而 LPP(Low Power Plus)指成熟的低功耗工藝,而適用于移動設備的 LP 系列其實還包含 LPC、LPU 。而且這些后綴并不是10nm 專屬,三星 FinFET 工藝都是這樣的命名方式,比如14nm FinFET 中,驍龍820是 LPP,而驍龍821則是 LPU。

并且除了 LP 系列之外,當然還有主打高性能的 HP(High Performance)系列, 這其中又分為很多種,這里就不展開講了。但是這也只是三星芯片的劃分方法,像臺積電雖然也是 FinFET 工藝,但是卻分為了FinFET Plus、FinFET Compact 等幾種。

生產的秘密:光刻機被卡脖子啦!

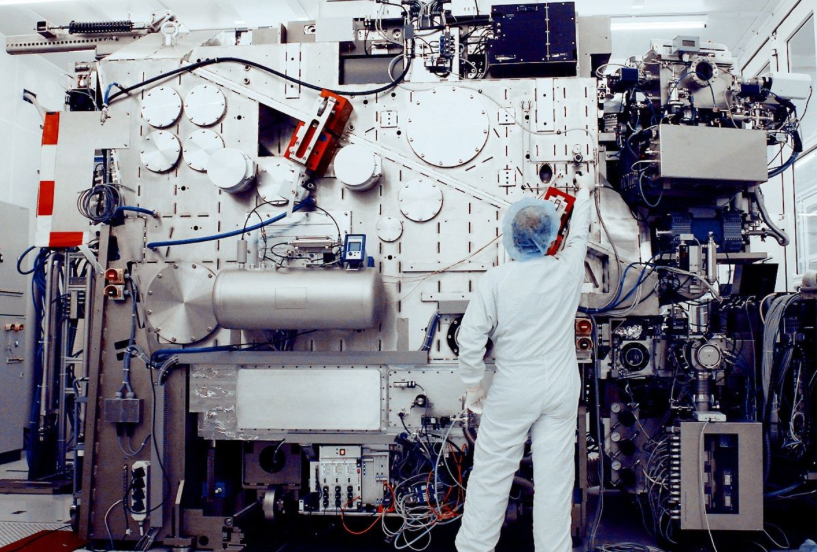

說完了技術,我們最后不如落到生產上聊一聊?畢竟隨著工藝的提升,對于生產設備的要求也越來越高了,過去各家在蝕刻晶圓的過程中用的都是深紫外光微影系統(tǒng),簡稱 DUV,而隨著制程超過10nm,現(xiàn)在 DUV 已經滿足不了精度要求,這時極紫外光微影系統(tǒng)(EUV)就上線了。

說到 EUV 是不是覺得很眼熟?沒錯,不久前三星剛剛以1.5億歐元每臺的價格從 ASML 訂購了10臺 EUV ,然而 ASML 這么久也一共才生產了23臺,很顯然,三星是想在 8nm/7nm 時代搶占先機。這已經不是他們第一次這么做了,當初在 OLED 的發(fā)展初期,他們就買走了市面上僅有7臺蒸鍍機中的5臺(蒸鍍是OLED 生產中的重要步驟),借此延緩了 LG 和京東方的 OLED 生產計劃。

總而言之,現(xiàn)在半導體行業(yè)在進入10nm 時代之后,無疑將會面臨制程、工藝以及生產的三重挑戰(zhàn),未來三星、臺積電和 Intel 是會繼續(xù)三足鼎立,還是會有人舊人掉隊、新人加入呢?我們拭目以待!

2017-11-39 來源:鳳凰網科技

文章關鍵詞: 韋爾股份 香港華清電子(集團)有限公司 半導體