芯片研發(fā)及生產(chǎn)全過程

人類對視覺信號天生的敏感決定了對圖形處理硬件性能的渴求成了現(xiàn)階段硬件產(chǎn)業(yè)最炙手可熱的話題。 與滿足聽覺的音頻設(shè)備相比,現(xiàn)在的圖形處理技術(shù)水平給圖形處理還留有很大的發(fā)展空間, 這就決定了這個(gè)產(chǎn)業(yè)的競爭充滿了變數(shù),在技術(shù)開發(fā)和市場推廣策略上稍有不慎就會(huì)別別人趕超。 為了應(yīng)付激烈的行業(yè)競爭, 設(shè)計(jì)出更高性能的圖形處理芯片已經(jīng)成為各個(gè)廠商保持自身競爭力水平最重要的手段。 今天我就來大家做一次特殊的旅行,了解圖形芯片設(shè)計(jì)研發(fā)的全過程,事實(shí)上現(xiàn)在絕大多數(shù)的芯片設(shè)計(jì)廠商都是依照這個(gè)程序來進(jìn)行新品研發(fā)的。

芯片,英文為Chip;芯片組為Chipset。芯片一般是指集成電路的載體,也是集成電路經(jīng)過設(shè)計(jì)、制造、封裝、測試后的結(jié)果,通常是一個(gè)可以立即使用的獨(dú)立的整體?!靶酒焙汀凹呻娐贰边@兩個(gè)詞經(jīng)常混著使用,比如在大家平常討論話題中,集成電路設(shè)計(jì)和芯片設(shè)計(jì)說的是一個(gè)意思,芯片行業(yè)、集成電路行業(yè)、IC行業(yè)往往也是一個(gè)意思。實(shí)際上,這兩個(gè)詞有聯(lián)系,也有區(qū)別。集成電路實(shí)體往往要以芯片的形式存在,因?yàn)楠M義的集成電路,是強(qiáng)調(diào)電路本身,比如簡單到只有五個(gè)元件連接在一起形成的相移振蕩器,當(dāng)它還在圖紙上呈現(xiàn)的時(shí)候,我們也可以叫它集成電路,當(dāng)我們要拿這個(gè)小集成電路來應(yīng)用的時(shí)候,那它必須以獨(dú)立的一塊實(shí)物,或者嵌入到更大的集成電路中,依托芯片來發(fā)揮他的作用;集成電路更著重電路的設(shè)計(jì)和布局布線,芯片更強(qiáng)調(diào)電路的集成、生產(chǎn)和封裝。而廣義的集成電路,當(dāng)涉及到行業(yè)(區(qū)別于其他行業(yè))時(shí),也可以包含芯片相關(guān)的各種含義。

芯片也有它獨(dú)特的地方,廣義上,只要是使用微細(xì)加工手段制造出來的半導(dǎo)體片子,都可以叫做芯片,里面并不一定有電路。比如半導(dǎo)體光源芯片;比如機(jī)械芯片,如MEMS陀螺儀;或者生物芯片如DNA芯片。在通訊與信息技術(shù)中,當(dāng)把范圍局限到硅集成電路時(shí),芯片和集成電路的交集就是在“硅晶片上的電路”上。芯片組,則是一系列相互關(guān)聯(lián)的芯片組合,它們相互依賴,組合在一起能發(fā)揮更大的作用,比如計(jì)算機(jī)里面的處理器和南北橋芯片組,手機(jī)里面的射頻、基帶和電源管理芯片組。

確定研發(fā)方案和硬件語言描述

與任何一個(gè)靠生產(chǎn)產(chǎn)品謀求發(fā)展的企業(yè)一樣,設(shè)計(jì)推出一款新的 GPU 的第一步理所當(dāng)然的是市場的調(diào)研和產(chǎn)品的開發(fā)規(guī)劃。在這段時(shí)間內(nèi),未來產(chǎn)品的相關(guān)定位,主要占領(lǐng)的市場范圍等話題都被提到桌面上討論,這些問題討論的結(jié)果最終將決定產(chǎn)品最終的研發(fā)方案的大體內(nèi)容:研發(fā)成本,研發(fā)周期以及開發(fā)過程中需要的資源等等。

接下來就要在研發(fā)方案確定的大方向的技術(shù)上研究從生產(chǎn)工藝,芯片代工等具體的細(xì)節(jié)問題進(jìn)行商議。在成本的限制范圍內(nèi)決定諸如集成晶體管數(shù)量等物理參數(shù);緊接著就要在符合生產(chǎn)工藝的芯片代工廠中做出選擇了,決定這個(gè)的因素很多,當(dāng)然第一點(diǎn)是能提供生產(chǎn)芯片要求的工藝水平,比如0.15微米,0.13微米,甚至90納米,其次是代工廠的產(chǎn)品質(zhì)量和價(jià)格因素。當(dāng)然很多時(shí)候芯片在設(shè)計(jì)的時(shí)候就計(jì)劃使用比較超前的工藝,保證選擇的代工廠(即芯片生產(chǎn)的公司比如TSMC )在芯片設(shè)計(jì)完成開始投片的時(shí)候完成相關(guān)工藝改造是十分重要的,如果你在這一點(diǎn)上面做出錯(cuò)誤的判斷,那對公司造成的損失是巨大的,因?yàn)閳D形芯片行業(yè)是一個(gè)最求速度的產(chǎn)業(yè),在生產(chǎn)工藝已經(jīng)決定的情況下,如果要在回過頭來修訂工藝指標(biāo),那進(jìn)行的工作又會(huì)持續(xù)幾個(gè)月,其中的工作量不比重新一塊芯片要少多少!

當(dāng)這一切前期環(huán)節(jié)確定以后,就開始我們這篇文章最主要的部分了,顯示芯片構(gòu)架的設(shè)計(jì)。一個(gè)設(shè)計(jì)團(tuán)隊(duì)被組織起來定義GPU 支持的技術(shù)特征并且制定整個(gè)設(shè)計(jì)工作的日程表(比如團(tuán)隊(duì)1在三周內(nèi)完成反鋸齒單元的設(shè)計(jì))。

在我們深入介紹芯片的設(shè)計(jì)過程之前,我們先來了解一下現(xiàn)在芯片制造公司一般的設(shè)計(jì)流程。 現(xiàn)在,芯片構(gòu)架的設(shè)計(jì)一般是通過專門的硬件設(shè)計(jì)語言Hardware DescripTIon Languages (HDL)來完成,所謂硬件設(shè)計(jì)語言( HDL)顧名思義,是一種用來描述硬件工作過程的語言。現(xiàn)在被使用的比較多的有 Verilog 、 VHDL。 這些語言寫成的代碼能夠用專門的合成器生成邏輯門電路的連線表和布局圖,這些都是將來發(fā)給芯片代工廠的主要生產(chǎn)依據(jù)。對于硬件設(shè)計(jì)語言( HDL)一般的人都基本上不會(huì)接觸到,我們在這里只給大家簡略的介紹一下:在程序代碼的形式上HDL和C也沒有太大的不同,但他們的實(shí)際功能是完全的不同。比如下面這個(gè)Verilog語言中非常基本的一條語句:

always@(posedge clock) Q 《= D;

這相當(dāng)于C里面的一條條件判斷語句,意思就是在時(shí)鐘有上升沿信號的時(shí)候,輸出信號 ‘D’ 被儲(chǔ)存在‘Q’。 就是通過諸如此類的語句描述了觸發(fā)器電路組成的緩存和顯存之間數(shù)據(jù)交換的基本方式。綜合軟件就是依靠這些代碼描述出來的門電路的工作方式關(guān)系生成電路的。在芯片的設(shè)計(jì)階段基本上都是通過工程師們通過Verilog語言編制HDL代碼來設(shè)計(jì)芯片中的所有工作單元,也決定該芯片所能支持的所有技術(shù)特征。這個(gè)階段一般要持續(xù)3到4個(gè)月(這取決于芯片工程的規(guī)模),是整個(gè)設(shè)計(jì)過程的基礎(chǔ)。

在上述的工作完成后,就進(jìn)入了產(chǎn)品設(shè)計(jì)的驗(yàn)證階段,一般也有一兩個(gè)月的時(shí)間。這個(gè)階段的任務(wù)就是保證在芯片最后交付代工廠的設(shè)計(jì)方案沒有缺陷的,就是我們平時(shí)所說的產(chǎn)品的“bug”。這一個(gè)階段對于任何芯片設(shè)計(jì)公司來說都是舉足輕重的一步,因?yàn)槿绻酒O(shè)計(jì)在投片生產(chǎn)出來以后驗(yàn)證出并不能像設(shè)計(jì)的那樣正常工作,那就不僅意味著繼續(xù)投入更多的金錢修改設(shè)計(jì),重新投片,還會(huì)在圖形芯片產(chǎn)業(yè)最為重視的產(chǎn)品推出速度方面失去先機(jī)。整個(gè)驗(yàn)證工作分為好幾個(gè)過程,基本功能測試驗(yàn)證芯片內(nèi)的所有的門電路能正常工作,工作量模擬測試用來證實(shí)門電路組合能達(dá)到的性能。當(dāng)然,這時(shí)候還沒有真正物理意義上真正的芯片存在,這些所有的測試依舊是通過HDL 編成的程序模擬出來的。

接下來的驗(yàn)證工作開始進(jìn)行分支的并行運(yùn)作,一個(gè)團(tuán)隊(duì)負(fù)責(zé)芯片電路的靜態(tài)時(shí)序分析,保證成品芯片能夠達(dá)到設(shè)計(jì)的主頻 ;另外一個(gè)主要由模擬電路工程師組成的團(tuán)隊(duì)進(jìn)行關(guān)于儲(chǔ)存電路,供電電路的分析修改。 和數(shù)字電路的修正工作相比,模擬工程師們的工作要辛苦的多,他們要進(jìn)行大量的復(fù)數(shù),微分方程計(jì)算和信號分析,即便是借助計(jì)算機(jī)和專門的軟件也是一件很頭疼的事情。同樣,這時(shí)候的多有測試和驗(yàn)證工作都是在模擬的狀態(tài)下進(jìn)行的,最終,當(dāng)上述所有的工作完成后,一份由綜合軟件生成的用來投片生產(chǎn)門電路級別的連線表和電路圖就完成了。 但是,圖形芯片設(shè)計(jì)者不會(huì)立即把這個(gè)方案交付廠家,因?yàn)樗€要接受最后一個(gè)考驗(yàn),那就是我們通常所說的FPGA (Field Programmable Gate Array)現(xiàn)場可編程門陣列來對設(shè)計(jì)進(jìn)行的最終功能進(jìn)行驗(yàn)證。 對于NV30那樣集成一億多個(gè)晶體管超級復(fù)雜芯片,在整個(gè)使用硬件設(shè)計(jì)語言( HDL)設(shè)計(jì)和模擬測試的過程中,要反復(fù)運(yùn)行描述整個(gè)芯片的數(shù)十億條的指令和進(jìn)行真正“海量”的數(shù)據(jù)儲(chǔ)存,因此對執(zhí)行相關(guān)任務(wù)的的硬件有著近乎變態(tài)的考驗(yàn)。我們從下面NVIDIA實(shí)驗(yàn)室的配備可見一斑。

可編程門陣列FPGA模擬驗(yàn)證

現(xiàn)場可編程門陣列FPGA可以能完成任何數(shù)字器件的功能,上至高性能CPU下至簡單的74電路,都可以用它來實(shí)現(xiàn)。FPGA其實(shí)是一個(gè)包含有大量門電路的邏輯元件,但是它的每一個(gè)門的定義可以有使用者來定義,如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入法,或是硬件描述語言自由的設(shè)計(jì)一個(gè)數(shù)字系統(tǒng)。通過軟件仿真,我們可以事先驗(yàn)證設(shè)計(jì)的正確性。在PCB完成以后,還可以利用FPGA的在線修改能力,隨時(shí)修改設(shè)計(jì)而不必改動(dòng)硬件電路。所以說使用FPGA來開發(fā)數(shù)字電路,可以大大縮短設(shè)計(jì)時(shí)間,更為重要的是大大減少了再出現(xiàn)成品芯片以后反復(fù)修改,投片資金和時(shí)間的消耗,一塊幾千美元的FPGA(這里指目前最大容量的FPGA)和花費(fèi)數(shù)百萬美元得到一塊成品芯片相比,消耗是微不足道的。

在這個(gè)方面,ATI 和 NVIDIA 公司都使用了名為IKOS的FPGA驗(yàn)證系統(tǒng)。 IKOS內(nèi)部是由多塊插卡構(gòu)成,每塊插卡都是一個(gè)FPGA陣列,由許多塊大規(guī)模FPGA組成。 因?yàn)榈搅薘300和NV30世代,圖形芯片已經(jīng)成了最復(fù)雜的ASIC芯片了,無法用一兩塊FPGA就能完成驗(yàn)證工作,必須使用這樣的專業(yè)FPGA驗(yàn)證設(shè)備。 當(dāng)然, FPGA也不是完美無缺的,它固有的缺點(diǎn)就是運(yùn)行速度還沒有ASIC芯片這么快。 和現(xiàn)在動(dòng)不動(dòng)運(yùn)行頻率都在200-300MHz 的GPU相比,IKOS 的運(yùn)行主頻大概只有可憐的幾十兆Hz左右。當(dāng)然這些缺點(diǎn)在應(yīng)用在產(chǎn)品的設(shè)計(jì)過程中沒什么大不了的。它負(fù)責(zé)的工作就是最終驗(yàn)證芯片設(shè)計(jì)功能的實(shí)現(xiàn),你可以讓IKOS作為顯示部分的系統(tǒng)正常運(yùn)行,進(jìn)行驅(qū)動(dòng)程序的開發(fā)和驗(yàn)證,當(dāng)然如果你硬要在這樣的系統(tǒng)上運(yùn)行游戲也不是不可能,不過能維持在每秒幾幀就不錯(cuò)了。

投片生產(chǎn)樣片和修正

經(jīng)過前面一系列的驗(yàn)證工作,這道工序就可以告一段落了,幾經(jīng)修訂的設(shè)計(jì)方案被送到了芯片代工廠開始投片生產(chǎn)。代工廠從拿到設(shè)計(jì)方案到第一批產(chǎn)品下線一般需要四周的時(shí)間,不過在這段時(shí)間里,設(shè)計(jì)人員仍舊馬不停蹄,繼續(xù)進(jìn)行芯片的模擬測試和上市產(chǎn)品PCB(Printed Circuit Boards印刷電路板) 的設(shè)計(jì),這就產(chǎn)生了一般官方欽定的“公板”。四周以后,第一批產(chǎn)品下線了,這就是我們一般稱為的”A0”版本。 (編者:就是常說的“工程樣片”)

一般情況下, A0版本的產(chǎn)量不會(huì)很多,它們的主要用途還是用來進(jìn)行測試和修改,一些被送到開發(fā)小組繼續(xù)測試和查錯(cuò),另一部分被送到相關(guān)的卡板廠商處進(jìn)行相關(guān)的測試和設(shè)計(jì)。由于現(xiàn)在是有了真正的芯片到手了,查錯(cuò)的手段當(dāng)然也要和前面的模擬手段不同。FIB (Focused Ion Beam聚焦離子束) 系統(tǒng)在這里被引入查錯(cuò)過程。簡單的說FIB系統(tǒng)相當(dāng)于我們平時(shí)在醫(yī)院看到的各種依靠波束能量進(jìn)行外科類手術(shù)的儀器,它們能在不破壞芯片功能的前提下,對芯片進(jìn)行門電路級別的修改——切斷原有的或者是布置新的門連線,不管你需要修改的電路是在芯片金屬布線的哪一層,也不會(huì)對芯片造成任何的物理損壞。

當(dāng)然,除了FIB設(shè)備外,還要使用很多其他的測試手段,像上圖這臺(tái)機(jī)器同樣是一臺(tái)探測芯片缺陷的設(shè)備,工作原理又完全不同,實(shí)際上它是一臺(tái)高性能原子級別電子顯微鏡。下面這張圖顯示的就是一塊NVIDIA 芯片在45,000X放大倍數(shù)下的面目。 我們在下圖中用紅線框圍繞的部分就是該芯片的缺陷。一般這種缺陷都是在生產(chǎn)過程中造成的, 由于某種其他物質(zhì)的原子混進(jìn)高純度硅晶體中造成的。這臺(tái)機(jī)器能夠辨別出混入的這種原子的種類并且判斷可能是什么原因這些原子會(huì)進(jìn)入到芯片的這個(gè)部分,從而能采取措施避免這種情況的發(fā)生,改善成品率。

當(dāng)“所有”的缺陷都得到了修正之后,最終的設(shè)計(jì)被交付到代工廠進(jìn)行投片生產(chǎn),這時(shí)的產(chǎn)量就不會(huì)像A0版本那么少了,但也不是最終的量產(chǎn)版本,在前面驗(yàn)證基本功無誤的情況下,這次生產(chǎn)的芯片要進(jìn)行各種各樣的和正式上市產(chǎn)品相關(guān)的測試:產(chǎn)品兼容性,工作溫度,外圍供電電路的穩(wěn)定性,信號完整性等等,直到產(chǎn)品能達(dá)到作為產(chǎn)品上市的程度,這時(shí)芯片生產(chǎn)方就可以投入量產(chǎn)了。

在最后的這些測試過程中,要測試大量的GPU,方便期間,顯卡上面都做出了GPU的插座,一個(gè)個(gè)獨(dú)立的GPU芯片只要插接在上面就能進(jìn)行測試了。當(dāng)然這些插座都是為特定的GPU芯片所設(shè)計(jì)的,只能來測試引腳定義相同的GPU。也許有朋友說,要是現(xiàn)在市面上的顯卡也做成這種插座式的設(shè)計(jì),并且能夠不斷進(jìn)行升級該有多好,我們先不說每一款芯片針腳定義不同。假設(shè)這方面不是問題,那我們至少也要保證顯存有能力向新核心提供數(shù)據(jù)的帶寬同步增長才有意義。所以說,顯卡上GPU插座的設(shè)計(jì)注定只能存在在實(shí)驗(yàn)室。

其實(shí)芯片設(shè)計(jì)過程中的插座原則也適用于其它產(chǎn)品,在主板 芯片組 的測試過程中也很常見,瞧瞧上面這塊nForce 2主板,它的 北橋 芯片同樣是安放在插座上的,當(dāng)然這是題外話了。

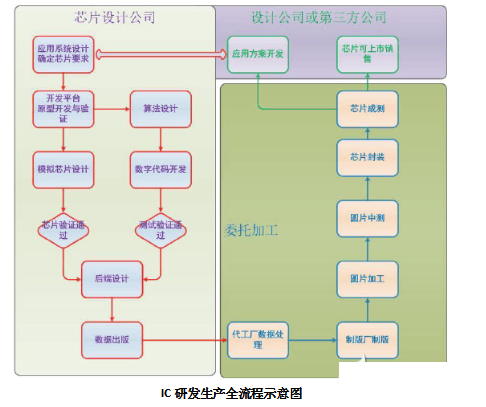

芯片研發(fā)基本過程

一款芯片的設(shè)計(jì)開發(fā),首先是根據(jù)產(chǎn)品應(yīng)用的需求,設(shè)計(jì)應(yīng)用系統(tǒng),來初步確定應(yīng)用對芯片功能和性能指標(biāo)的要求,以及哪些功能可以集成,哪些功能只能外部實(shí)現(xiàn),芯片工藝及工藝平臺(tái)的選擇,芯片管腳數(shù)量,封裝形式等等,達(dá)到整個(gè)應(yīng)用系統(tǒng)的成本低性能高,達(dá)到最優(yōu)的性價(jià)比。

之后,進(jìn)入系統(tǒng)開發(fā)和原型驗(yàn)證階段。根據(jù)芯片的框架結(jié)構(gòu),采用分立元件設(shè)計(jì)電路板,數(shù)字系統(tǒng)一般用FPGA開發(fā)平臺(tái)進(jìn)行原型開發(fā)和測試驗(yàn)證(常見的FPGA有XILINX和ALTERA兩個(gè)品牌,我公司用的是XILINX)。

模擬芯片的設(shè)計(jì),驗(yàn)證手段主要是根據(jù)工藝廠提供的參數(shù)模型來仿真,最終能達(dá)到的性能指標(biāo)只能通過真實(shí)的投片,進(jìn)行驗(yàn)證設(shè)計(jì);而數(shù)字系統(tǒng)設(shè)計(jì)一般可通過計(jì)算機(jī)仿真和FPGA系統(tǒng),進(jìn)行充分的設(shè)計(jì)驗(yàn)證,然后可以直接投片。因此數(shù)?;旌系男酒a(chǎn)品開發(fā),一般需要模擬模塊先投片驗(yàn)證,性能指標(biāo)測試通過后,然后再進(jìn)行整體投片。

系統(tǒng)開發(fā)和原型驗(yàn)證通過后,就進(jìn)入芯片版圖的設(shè)計(jì)實(shí)現(xiàn)階段,就是數(shù)字后端、與模擬版圖拼接。版圖設(shè)計(jì)過程中,要進(jìn)行設(shè)計(jì)驗(yàn)證,包括DRC、LVS、ANT、后仿真等等。芯片版圖通過各種仿真驗(yàn)證后就可以生成GDS文件,發(fā)給代工廠(或者制版廠),就是常說的tapeout了。

代工廠數(shù)據(jù)處理,拿到GDS數(shù)據(jù)后,需要再次進(jìn)行DRC檢查,然后數(shù)據(jù)處理,版層運(yùn)算,填充測試圖形等操作,之后發(fā)給制版廠開始制版。

制版完成后,光刻版交給代工廠就可以進(jìn)行圓片加工了。

圓片加工完成后,送至中測廠進(jìn)行中測,也叫晶圓測試(Chip Test,簡稱CP)。中測完成,圓片上打點(diǎn)標(biāo)記失效的管芯,交給封裝廠。

封裝廠進(jìn)行圓片減薄、貼膜、劃片、粘片、打線、注塑、切金、烘干、鍍錫等等操作后,封裝完成。目前封裝技術(shù)比較成熟,常見封裝良率在99.5%以上,甚至99.9%以上。

芯片有些功能和性能在中測時(shí)無法檢驗(yàn)的,需要進(jìn)行成測(Final Test,簡稱FT)。 成測完成的芯片,即可入產(chǎn)品庫,轉(zhuǎn)入市場銷售了。

芯片的研發(fā)過程,是一個(gè)多次循環(huán)迭代的過程。測試驗(yàn)證過程中發(fā)現(xiàn)問題,就需要返回修改設(shè)計(jì),然后再次測試驗(yàn)證;后端版圖實(shí)現(xiàn)過程中,如果時(shí)序、功耗、面積、后仿真等通不過,也可能要返回原始設(shè)計(jì)進(jìn)行修改;芯片投片出來后,測試性能指標(biāo)和可靠性達(dá)不到設(shè)計(jì)要求,需要分析定位問題,修改設(shè)計(jì),再次投片驗(yàn)證,等等。

芯片研發(fā)環(huán)節(jié)多,投入大,周期長。任何一個(gè)細(xì)節(jié)考慮不到或者出錯(cuò),都有可能導(dǎo)致投片失?。患夹g(shù)研發(fā)充滿了不確定性,可能導(dǎo)致時(shí)間拖延及投片失敗。因此,一個(gè)成熟產(chǎn)品的研發(fā),可能需要多次的投片驗(yàn)證,導(dǎo)致周期很長。

現(xiàn)在芯片設(shè)計(jì)的規(guī)模比較大,系統(tǒng)復(fù)雜,為了減小投片風(fēng)險(xiǎn),系統(tǒng)設(shè)計(jì)和測試驗(yàn)證的工作十分重要,一方面依靠強(qiáng)大的EDA工具,另一方面依靠經(jīng)驗(yàn)和人員時(shí)間投入。

芯片轉(zhuǎn)入量產(chǎn)后,如果成品率不穩(wěn)定或低于預(yù)期,需要與代工廠分析原因,進(jìn)行工藝參數(shù)調(diào)整,多次實(shí)驗(yàn)后,找到最穩(wěn)定的工藝窗口,提高芯片的可靠性和良率,降低成本。

常見的芯片投片方式說明

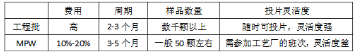

芯片常用投片方式有工程批(FULLMASK)和多項(xiàng)目晶圓(MulTI Project Wafer,簡稱MPW)兩種方式。

隨著制造工藝水平的提高,在生產(chǎn)線上制造芯片的費(fèi)用不斷上漲,一次0.6微米工藝的工程批生產(chǎn)費(fèi)用就要20-30萬元,而一次0.18微米工藝的工程批生產(chǎn)費(fèi)用則需要60-120萬元,如果采用高階工藝,試驗(yàn)片成本更會(huì)呈幾何倍數(shù)提高。如果設(shè)計(jì)中存在問題,那么制造出來的所有芯片將全部報(bào)廢。

MPW就是將多個(gè)具有相同工藝的集成電路設(shè)計(jì)放在同一晶圓片上流片,流片后,每個(gè)設(shè)計(jì)品種可以得到幾十片芯片樣品,這一數(shù)量對于設(shè)計(jì)開發(fā)階段的實(shí)驗(yàn)、測試已經(jīng)足夠。而實(shí)驗(yàn)費(fèi)用就由所有參加MPW的項(xiàng)目按照芯片面積分?jǐn)偅杀緝H為工程批的10%-20%,極大地降低新產(chǎn)品開發(fā)成本和開發(fā)風(fēng)險(xiǎn)。MPW一般由工藝廠組織,每年定期有班次。

雖MPW降低了集成電路研發(fā)階段的費(fèi)用門檻,但也伴隨著一些投片靈活度低、生產(chǎn)周期長、單位面積有限制等制約因素。具體的投片方式,需要根據(jù)設(shè)計(jì)成功率、資金預(yù)算、時(shí)間周期來具體選擇。兩種投片方式對比表:

研發(fā)一款新的顯卡的過程真好比“萬里長征”一般,講的小編都有些疲憊了,更不要講參與研發(fā)的那些工程師們所要付出辛勞和智慧了。而通過整個(gè)產(chǎn)品研發(fā)有條不紊,環(huán)環(huán)相扣的程序制定,我們也看到了西方工業(yè)在科學(xué)理論系統(tǒng)化和產(chǎn)業(yè)化方面的強(qiáng)大能量,這也是我們值得學(xué)習(xí)的啊。

2017-12-15 來源:EEFOCUS 與非網(wǎng)