AI開始在芯片設(shè)計領(lǐng)域大顯身手

來源:本文由eetimes,eettaiwan 翻譯,謝謝。

業(yè)界供應(yīng)商和研究人員最近在將機器學習應(yīng)用于棘手的芯片設(shè)計問題方面取得了重大的進展。從今年DesignCon大會上的一場專題討論就可看出,在電子設(shè)計自動化(EDA)方面使用人工智能(AI)是目前十分熱門的主題,不僅在本屆大會上有多篇相關(guān)論文發(fā)表,專題討論時也吸引眾多與會者,現(xiàn)場座無虛席。

過去一年來,機器學習實現(xiàn)先進電子研究中心(CAEML)又增加了四家新的合作伙伴。這個由13家業(yè)界成員和3所大學共同組成的研究團隊,目前正持續(xù)擴大其工作的廣度和深度。

惠與科技(Hewlett-Packard Enterprise;HPE)杰出技術(shù)專家兼CAEML成員Christopher Cheng說:「去年,我們主要關(guān)注于訊號完整性和電源完整性,而在今年,我們將產(chǎn)品組合劃分為系統(tǒng)分析、芯片布局和可信任的平臺設(shè)計,讓研究的多樣性取得了最大的進展?!?

北卡羅來納州立大學(NC State University)杰出教授Paul Franzon表示:「貝葉斯(Bayesian)最佳化和卷積神經(jīng)網(wǎng)路(CNN)在可制造性設(shè)計(DFM)方面也顯著提升了功能,我們開始考慮在設(shè)計過程中使用同步學習。」北卡羅來納州立大學就是CAEML的三所合作院校之一。

另一所與CAMEL合作的學校——喬治亞理工學院(Georgia Institute of Technology)教授Madhavan Swaminathan說:「我們面臨的挑戰(zhàn)之一是取得公司的數(shù)據(jù)。因為他們的大部份數(shù)據(jù)都是專有的,因此我們經(jīng)提出了幾種處理機制。這些過程目前都運作得不錯,但仍然比我們預期的更長得多?!?

CAEML在成立之初就獲得了亞德諾半導體(ADI)、益華電腦(Cadence)、思科(Cisco)、IBM、輝達(Nvidia)、高通(Qualcomm)、三星(Samsung)和賽靈思( Xilinx)等九家廠商的支持,一開始感興趣領(lǐng)域包括高速互連、電力傳輸、系統(tǒng)級靜電放電、IP核心重用,以及設(shè)計規(guī)則檢查。

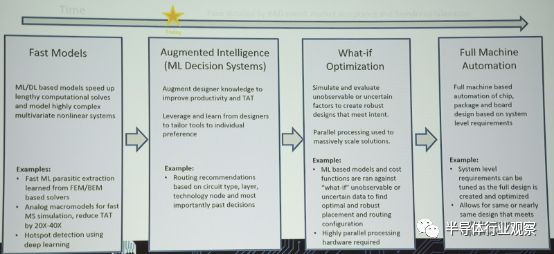

從Cadence描繪的發(fā)展藍圖來看,EDA產(chǎn)業(yè)目前開始進入AI應(yīng)用的第二階段(來源:Cadence)

Cadence Design Systems等EDA供應(yīng)商早在1990年代初就開始研究機器學習。Cadence研發(fā)部資深總監(jiān)David White表示,這項技術(shù)于2013年首次導入于其產(chǎn)品中,采用Virtuoso的一個版本,并利用分析和資料探勘為寄生參數(shù)擷取創(chuàng)建機器學習模型。

截至目前為止,Cadence已經(jīng)為其工具提供超過110萬種機器學習模型了,用于加速長時間的計算。下一個階段的產(chǎn)品開發(fā)就是布局與繞線工具,使其得以向人類設(shè)計師學習,并推薦可加速運轉(zhuǎn)時間的最佳化方案。White解釋,這些解決方案可能結(jié)合使用本地和基于云端的處理,以利用平行系統(tǒng)和大型資料集。

機器學習技術(shù)與應(yīng)用最新進展

Synopsys研發(fā)總監(jiān)Sashi Obilisetty表示,在先進制程節(jié)點上,采用現(xiàn)有演算法的全域繞線(global routing)工具已經(jīng)達到極限了,因此他們開始降低芯片數(shù)據(jù)速率,以實現(xiàn)時序收斂。

她補充說,臺積電(TSMC)去年使用機器學習預測全域繞線,使得速度提高了40MHz; Nvidia則用機器學習來提供芯片設(shè)計的全面覆蓋,同時減少模擬。

參加這場專題討論的專家們說,他們看到了業(yè)界存在著使用各種機器學習技術(shù)實現(xiàn)自動化特定決策和最佳化整體設(shè)計流程的許多機會。

具體而言,研究人員正探索以更快速度的AI模型取代當今模擬器的機會。喬治亞理工學院的Swaminathan說,相對較慢的模擬器可能導致計時錯誤、類比電路失調(diào),以及導致芯片重新流片(respin)的建模不足等問題。此外,機器學習可以取代IBIS在高速互連中進行行為建模。

除了由亞馬遜(Amazon)、Google和Facebook圖片搜索和語音辨識服務(wù)推廣的神經(jīng)網(wǎng)路模型以外,芯片研究人員也使用了資料探勘、統(tǒng)計學習和其他工具。

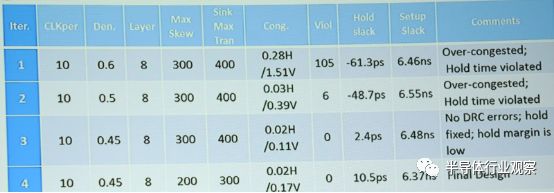

北卡羅來納州立大學的Franzon則報告使用代理模型,在4次迭代中實現(xiàn)最終實體設(shè)計最佳化,相形之下,工程師還必須進行到20次。類似的技術(shù) 被用于校準類比電路,并為多通道互連設(shè)置收發(fā)器。

研究人員展示代理模型在4次迭代中的表現(xiàn),可望取代人類設(shè)計師(20次)(來源:NC State University)

AI可以在EDA工具(有時是指旋鈕)中設(shè)置幾十種選項,協(xié)助加速自動化過程。Franzon說:「這些工具設(shè)置了一些有時候定義不清的旋鈕,經(jīng)常與預期結(jié)果之間的關(guān)系模糊?!?

HPE目前則結(jié)合使用神經(jīng)網(wǎng)路和超平面分類器,依據(jù)固態(tài)硬碟(SSD)的電壓、溫度和電流等數(shù)據(jù)現(xiàn)場預測故障情形。

Cheng說:「訓練所需的數(shù)據(jù)量龐大。到目前為止,分類器都是靜態(tài)的,但是我們希望增加使用遞歸神經(jīng)網(wǎng)路(RNN)的時間維度,以取代僅用好/壞標簽,那么我們將會有故障時間(time-to-failure)的標簽。未來,我們還希望將這項工作擴展到更多的參數(shù)以及一般的系統(tǒng)故障。」

2018-02-02 來源:半導體行業(yè)觀察